Physical Addressing

간단한 시스템에서 사용

ex) 자동차, 엘리베이터, 디지털 카메라 등

Virtual Addressing

최신 서버, 노트북, 스마트폰에서 사용

• Virtual Memory

메인 메모리를 스토리지의 캐시로 사용한다.

프로그램들은 메인 메모리를 공유한다.

각 프로그램은 자주 사용하는 코드와 데이터를 저장하는 개별 가상 주소 공간을 가진다.

메모리 참조 시 가상 주소를 사용한다.

가상 주소 공간은 다른 프로세스로부터 보호된다.

가상 메모리의 block은 page라고 한다.

주소 변환 실패는 Page fault라고 한다.

• Virtual Address

프로그램은 메모리의 어느 위치에든 배치될 수 있다.

여러 개의 프로그램이 동시에 수행될 수 있다.

Address Translatinon은 여러개의 프로그램이 각자의 Address Space를 보호하면서 메모리를 공유할 수 있도록 해준다.

하나의 프로그램에서 다른 프로그램을 전환하는 것을 Context Switch 라고 한다.

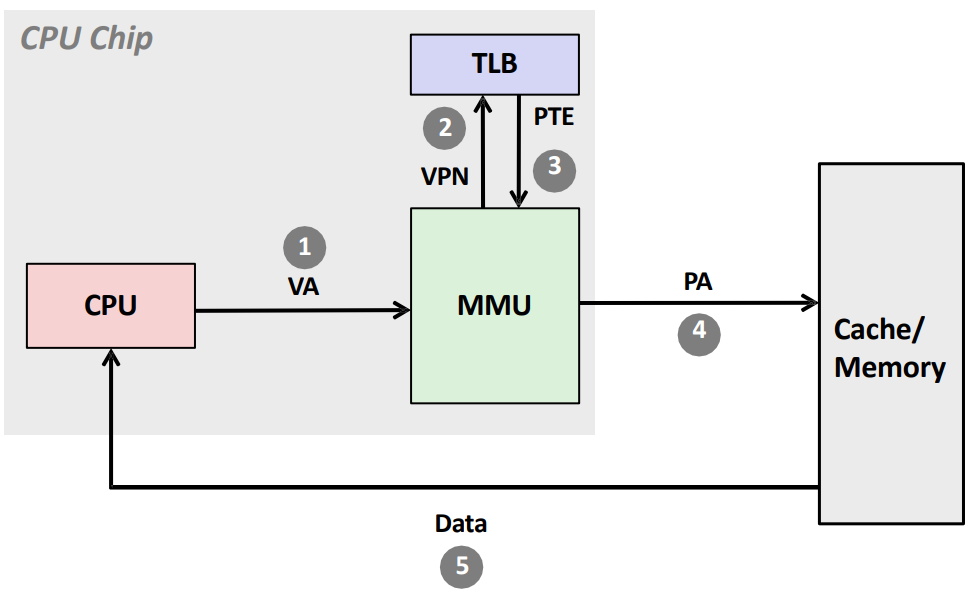

• Address Translation

Virtual Address를 Physical Address로 변환하는 것을 Translation이라고 한다.

Adress translation은 메모리 access를 할 때 마다 발생한다.

각 application은 각자 고유한 address space를 가진다.

MMU가 변환을 담당하고 있다.

(Memory Mangement Unit)

• Paging

Memory Fragmentation을 줄이기 위한 하나의 방법이다.

프로그램의 Data를 page라는 작은 고정된 사이즈로 쪼갠다.

ex) 4KB

어플리케이션은 모두 각각의 Page table을 가진다.

CPU가 가상 주소를 물리 주소로 변환할 때 페이지 번호를 페이지 테이블에서 조회한다.

페이지 테이블은 해당 해당 페이지의 물리 주소를 반환한다.

Page offset은 frame offset과 동일하게 처리된다.

• Page Table Structure

위의 그림에서 볼 수 있듯이 각 Process 별로 하나의 테이블을 보유하고 있다.

페이지 테이블은 주로 Physical Memory에 위치하는데, 이는 주로 메인 메모리에 저장된다.

이 때문에 cache를 활용하지 못해서 성능이 많이 떨어진다.

• Translation Process

Valid Page

권한 검사를 진행해 Access 권한이 있는 경우에만 Physical Address를 Return한다.

Invalid Page

Page가 현재 Page Table에 없으므로, Page Fault로 처리한다.

이 경우에 새로운 Page를 Storage에서 불러온 다음, Page Table에 새로운 Entry를 추가하고 명령어 실행을 다시 시작해야 한다.

• Improving Access Time

Locality를 활용하기 위해 Page Table 또한 Caching 한다.

여기서 활용하는 것을 TLB라고 한다.

TLB : Translation Lookaside Buffer(변환 색인 버퍼)

Cache 보다 작은 크기를 가지고 있고 Associativity를 높게 하는 것이 일반적이다.

용량이 작아 cache access 만큼 빠른 성능을 가지고 있다.

모든 메모리 접근은 TLB를 확인한다.

TLB Hit

메모리 엑세스가 발생하지 않는다.

TLB Miss

추가 메모리 엑세스가 발생한다.(Page table)

Page Faults

Page table에 원하는 translation이 없는 경우 Page fault가 발생한다.

한 그림으로 정리해보면 아래와 같다.

프로그램 성능에 무조건 영향을 줄 수밖에 없다는 사실을 알 수 있다.

• Memory Hierarchy Principles

메모리의 모든 계층구조에서 적용될 수 있는 공통 원칙을 정리해보자.

1. 블록 할당

블록 할당은 Assciativity에 의해 결정된다.

- Direct mapped (1-way associative) : 할당할 위치가 1개

- N-way set associative : Set 내에 N개의 선택지가 존재

- Fully associative : 캐시 내의 어디든 위치시킬 수 있음

높은 associativity는 miss rate를 줄이지만 하드웨어 복잡도, 비용, 접근 시간을 증가시킨다.

2. 블록 찾기

| Associativity | 위치 방법 | 태그 비교 횟수 |

| Direct mapped | 인덱스(Index) | 1 |

| n-way set associative | 집합 인덱스(Set index) 이후 집합 내의 항목 검색 |

n |

| Fully associative | 모든 항목 검색 | 항목 수(#entries) |

| Full lookup table | 0 |

하드웨어 캐시 구조

비교 횟수를 줄이면 비용을 절감할 수 있다.

가상 메모리

Full table lookup는 모든 페이지가 page table에 매핑될 수 있다.

miss rate를 줄이는 데 이점이 있다.

3. Miss인 경우, 교체 알고리즘

LRU

가장 오랫동안 사용되지 않은 블록을 교체한다.

높은 associativity인 경우, 하드웨어의 복잡도/비용이 증가한다.

Random

LUR와 비슷한 성능을 가지며 구현이 더 쉽다.

가상 메모리

하드웨어 지원을 통해 LUR을 근사화한다.

4. Write policy

- Write-through (즉시 쓰기)

데이터를 쓸때 Upper cache와 Lower cache 모두에 업데이트를 수행한다.

교체가 쉬워지나, 성능을 위해 write buffer를 필요로 한다. - Write-back (나중 쓰기)

데이터를 쓸때 upper cache (ex. L1 cache)에만 업데이트를 수행한다.

Uppper cache에만 자주 접근하기 때문에 성능이 향상된다.

더 많은 상태 정보 (Dirty 비트)를 저장해야 한다. - Virtual Memory

disk write latency(디스크 쓰기 지연) 때문에 Write-back만 사용이 가능하다.

Write-through는 디스크 쓰기 속도가 매우 느려진다.

결국 메모리 시스템 설계는 프로세서에 가장 중요한 부분임을 인지해야 한다!

'CS > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] #11 Memory(2) (0) | 2024.06.11 |

|---|---|

| [컴퓨터구조] #10 Memory(1) (0) | 2024.06.11 |

| [컴퓨터구조] #9 Pipeline (0) | 2024.06.09 |

| [컴퓨터구조] #8 Processor (0) | 2024.06.03 |

| [컴퓨터구조] #7 ISA(3) (0) | 2024.04.23 |