• Direct Mapped Problem

Conflict Miss가 계속 반복해서 일어날 가능성이 있다.

Block Size가 모두 4byte인 Extreme Case를 가정해보자.

Cache에 하나의 Entry만 있기 때문에 Conflict Miss가 끊임없이 발생하게 된다.

위와 같은 상황을 Trashing이라고 한다.

(Cache에 Data를 Loading하기 전에 반드시 원래 있던 Data를 쫓아내야 하는 상황)

• Fully Associative Cache

각 Entry에 모든 주소로부터 온 Data가 저장될 수 있도록 한다.

장점 : Conflict Miss가 발생하지 않고 Cache가 꽉 차서 발생하는 Miss인 Capacity Miss만 발생한다.

단점 : 모든 Entry의 Cache Tag를 비교해야 필요한 Data를 찾을 수 있다.

(오히려 성능이 떨어질 수 있다.)

만약 모든 Extreme한 Solution이 실용적이지 않아 보인다면, Hybrid Solution을 찾아라

Hybrid Solution인 N-Way Set Associative Cache에 대해 알아보자.

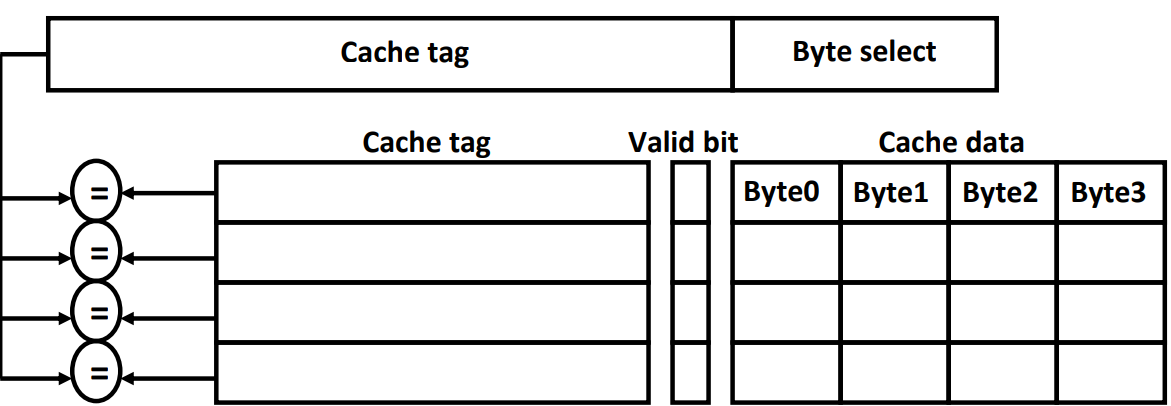

• N-Way Set Associative

N개의 Entry가 각 Index에 할당된다.

즉, N개의 Direct Mapped Cache가 병렬적으로 동작한다.

N-way Set Associative Cache는 한 세트에 최대 N개의 블록을 저장할 수 있다.

하나의 Set에 대해 N번의 Comparsion만 하면 된다.

Associative가 증가하면, miss rate가 줄어든다.

단점 : 추가적인 gate와 MUX가 필요하다.

N개 중 원하는 Data를 뽑아내기 위한 Extra MUX에서 발생하는 Delay가 Hit Time을 늘어나게 한다.

• Cache Block Replacement Policy

Direct-Mapped Cach

각 Memory Block은 오직 하나의 Cache Entry에만 존재할 수 있기 때문에, Replacement Policy가 필요없다.

N-way Set Associative Cache

Least Recently Used(LRU)가 사용된다.

(가장 오랜 시간 동안 사용하지 않은 Block을 먼저 교체하는 알고리즘)

Fully Associative

LRU를 사용할 경우 모든 접근 history를 다 저장해야 하기 때문에 굉장히 복잡하다.

• Cache Miss

Compulsory/Cold Start

초기 접근은 항상 Miss가 발생하기 마련이다.

가능한 Solution은 Cache Size를 늘리는 것이다.

Capacity

Cache는 program에 의해 사용되는 모든 Block을 저장할 수 없다.

가능한 Solution은 Cache Size를 늘리는 것이다.

Conflict

서로 다른 Memory 주소가 같은 Entry로 Mapping 되는 것이다.

가능한 Solution은 Cache size나 Associativity를 늘리는 것이다.

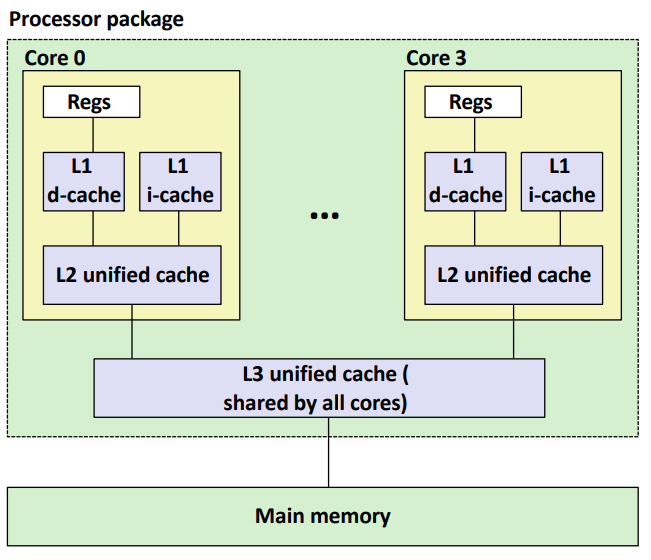

• Multilevel Caches

L1 캐시

크기가 작지만 매우 빠르다.

최소한의 Hit time을 달성하는 것에 중점을 둔다.

L2 캐시

L1 캐시의 미스를 처리하는 캐시이다.

L1 캐시보다 느리지만 메인 메모리보다는 빠르다.

낮은 Miss rate를 달성하는 것에 중점을 둔다.

메인 메모리

L2 캐시 미스를 처리하는 메모리이다.

매우 크며 접근 속도가 느리다.

L3

L2 캐시 미스를 처리하는 메모리이다.

L2 캐시보다 느리지만 메인 메모리보다는 빠르다.

• Cache Performance

숫자를 직접 넣어보면 알겠지만, L1 캐시는 작고 빠르지만, L2 캐시가 추가되면 전체 성능이 더 좋아진다.

또한 다중 레벨 캐시를 사용하면 메인 메모리 접근 시간을 줄여 CPU 성능을 향상시킬 수 있다.

결국 Cache를 최적하는 것이 중요하며, 소프트웨어 개발에서도 Cache를 간과해서는 안된다!

'CS > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] #12 Memory(3) (0) | 2024.06.11 |

|---|---|

| [컴퓨터구조] #10 Memory(1) (0) | 2024.06.11 |

| [컴퓨터구조] #9 Pipeline (0) | 2024.06.09 |

| [컴퓨터구조] #8 Processor (0) | 2024.06.03 |

| [컴퓨터구조] #7 ISA(3) (0) | 2024.04.23 |