이제 실제 프로세서로 구현하면 어떻게 될지 알아보도록 하자.

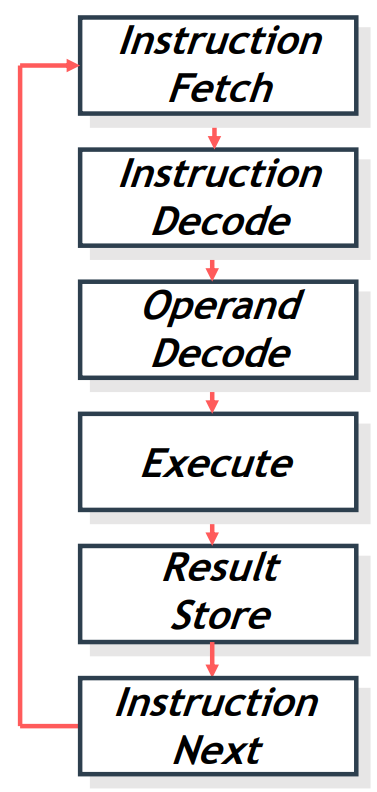

• Execution Cycle

Instruction Fetch(IF) : 메모리로부터 명령어를 가져온다.

Instruction Decode(ID) : 명령어를 해석해서 필요한 동작을 정의한다.

Operand Decode : Operand 데이터를 가져온다.

Execute(EX) : 명령어의 결과값/상태를 계산한다.

Result Store(MEM) : 결과값을 스토리지에 저장한다.

Instruction Next : 다음 명령어를 정의한다. (PC = PC+4)

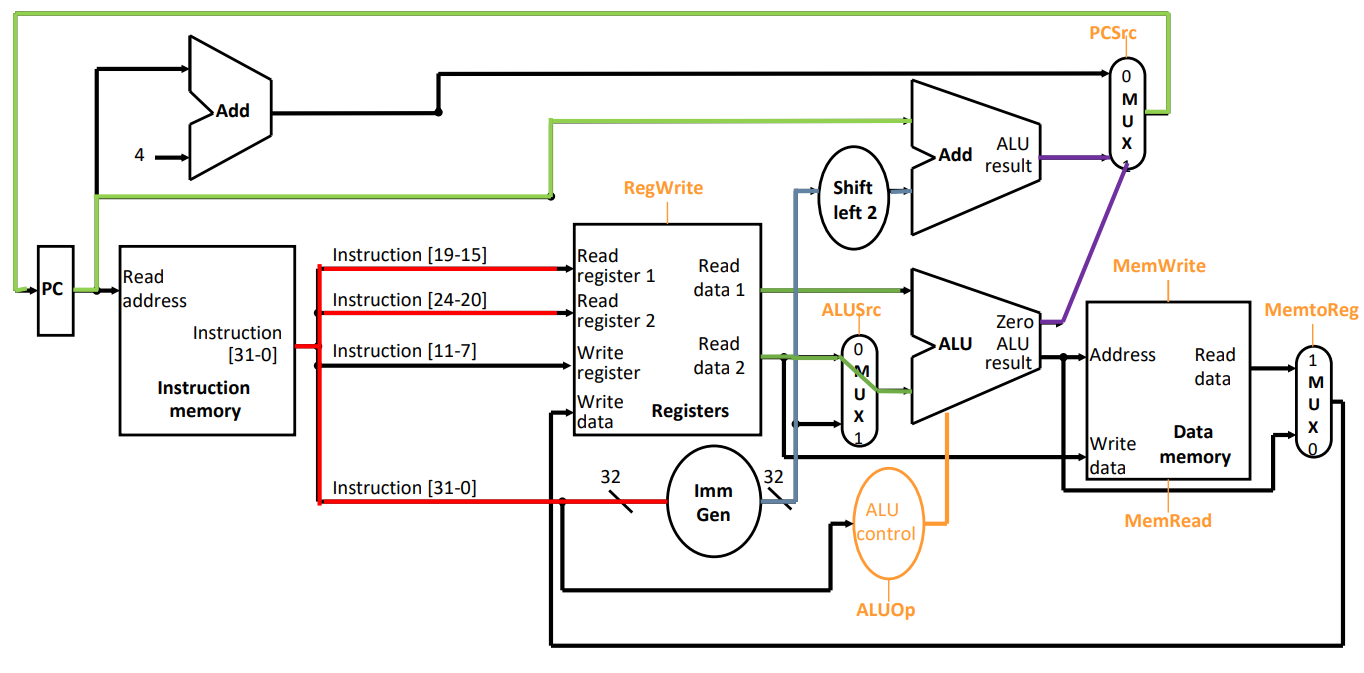

• Implementation Overview

메모리 및 FU를 통과하는 데이터의 흐름이다.

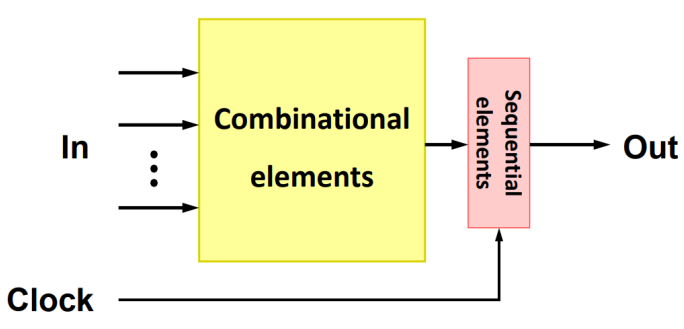

• Digital Systems

디지털 시스템을 구현하기 위해 필요한 3가지 컴포넌트들이 있다.

Combinational elements(조합 회로)

조합 회로는 현재 입력 값에만 의존하여 출력을 결정한다.

대표적으로 ALU(산술 논리 장치)가 있다.

Sequential elements(순차 회로)

순차 회로는 상태 정보를 저장할 수 있다.

대표적으로 Register(레지스터)가 있다.

내부에 상태 정보를 가지고 있어 시간의 흐름에 따라 상태가 변할 수 있다.

조합 회로와 순차 회로의 차이점은 Clock의 관여 유무에 있다.

Clock signals (클럭 신호)

메모리 요소의 업데이트를 조절하는 역할을 한다.

positive edge나 negative edge에서 순차 회로의 상태를 업데이트한다.

각 회로들에 대해 더 자세히 알아보도록 하자.

조합 회로

- 조합 회로는 논리 게이트들로 구성된 네트워크이며 비순환형 구조이다.

즉, 입력에서 출력으로 향하는 경로 중 순환 경로가 없다. - 입력 변경에 즉시 반응한다.

- 출력은 입력의 함수이다. (Output = f(input))

예시

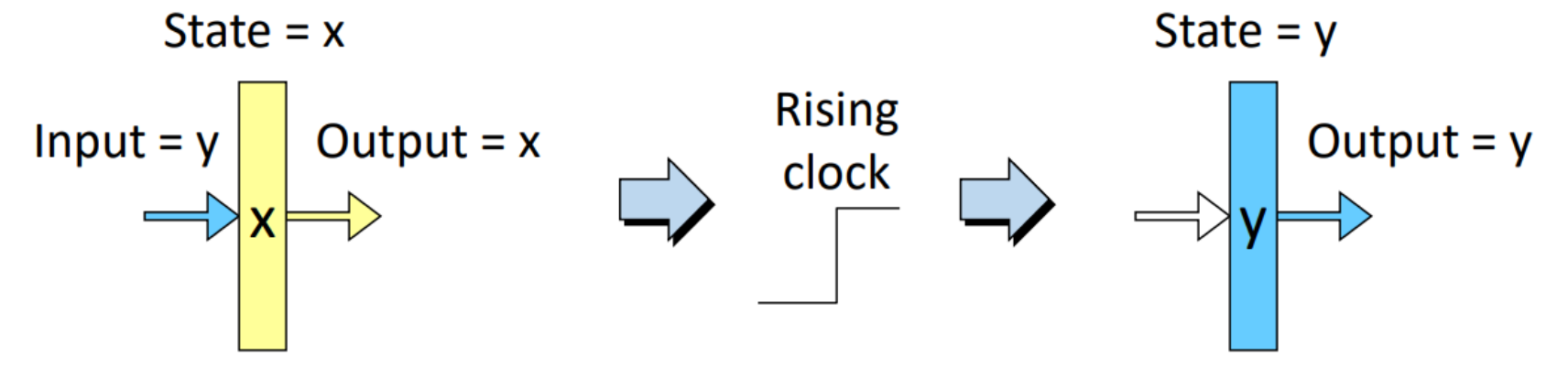

순차 회로

- Write 신호가 1일때 클럭 엣지에서 레지스터 값을 업데이트한다.

- 값을 저장하여 이후에 사용한다.

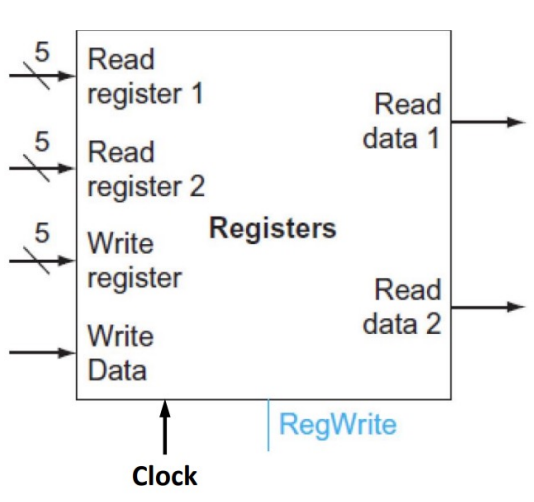

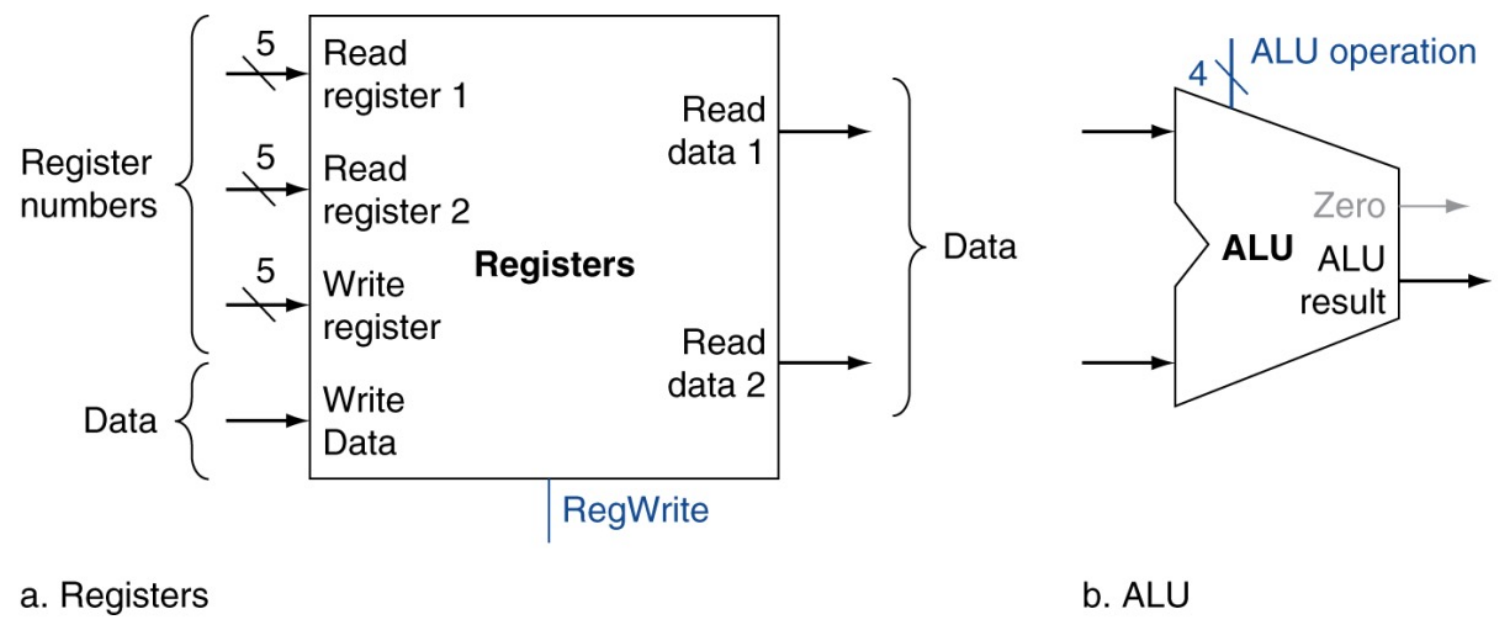

• 레지스터

레지스터 동작

레지스터는 데이터를 저장하고 필요할 때 이를 제공하는 순차회로이다.

클럭 신호에 의해 동작하며 intput과 output 사이의 차단기 역할을 한다.

레지스터 파일

레지스터 파일을 여러개의 레지스터가 모여 하나의 집합을 이루는 구조이다.

레지스터 파일은 여러개의 레지스터로 구성된다.

예를 들어, RISC-V 아키텍처에서는 32개의 레지스터(x0 ~ x31)가 사용된다.

레지스터 파일은 동시에 여러 데이터를 읽고 쓸 수 있는 여러 포트를 가지고 있다.

각 포트는 별도의 주소와 데이터 입력/출력을 사용한다.

데이터의 RegWrite 신호가 활성화(1)된 경우에만 레지스터에 기록된다.

레지스터 파일의 읽기와 쓰기

Reading(읽기)

조합 회로처럼 동작한다.

입력 신호에 기반하여 출력을 즉시 생성한다.

출력 데이터는 입력 주소가 설정된 후 일정 지연 시간이 지난 후에 제공된다.

Writing(쓰기)

레지스터의 동작과 유사하다.

클럭 신호의 positive edge에서만 발생한다.

• 데이터 메모리

데이터 메모리는 프로그램 데이터를 저장하기 위한 RAM이다.

레지스터와 유사한 동작을 한다.

읽기와 쓰기 모두 클럭 신호와 제어 신호에 의해 제어된다.

명령어를 위한 읽기 전용 메모리가 존재한다.

• Multiplexers

Multiplexer(MUX)는 여러 소스로부터 들어오는 디지털 신호들을 하나의 출력 신호로 나갈 수 있도록 해주는 장치이다.

쉽게 말해, 교통정리 해준다고 생각하면 된다!

따라서 어떤 input 신호가 output으로 나갈지 선택하는 시그널 (=selector)이 필요하다.

이제 Instruction들을 실제로 살펴보자.

• Instruction Fetch

Fetch는 PC값을 읽고, 명령어 메모리에서 명령어를 가져온 다음 PC값을 업데이트하는 순서로 진행된다.

ex) PC = PC+4(32 bit 명령어 기준)

• R-type Instruction

레지스터 3개가 사용된다고 가정하자.(add x10, x11, x12)

- 명령어에서 지정한 두개의 소스 레지스터에서 값을 읽는다.(x11, x12)

- ALU에서 add 명령어로 덧셈 연산을 수행한다.(x11 + x12)

- 연산 결과를 x10 레지스터에 저장한다.

이때, R-type 명령어는 ALU 연산을 수행한 후 그 결과를 목적지 레지스터에 저장해야 하므로 RegWrite 신호는 활성화 값(1)이 되어야 한다.

• Load/Store Instructions

Load 명령어(lw X10, 0(x11))을 사용한다고 하자.

- 레지스터 피연산자를 읽는다.

- 12 bit offset을 사용해 주소 계산을 한다.

- 계산된 주소에서 데이터를 읽어오고(Load) 저장한다.(Store)

명령어의 종류에 따라 MemWrite와 MemRead 중 하나가 활성화된다.

• Branch Instructions

bne x10, x11x 2000이라고 하자.

- rs1과 rs2 레지스터에서 값을 읽어온다

- ALU에서 두 값을 뺐을때 0이 되는지 판단한다.

0이면 계산된 target address에서 나온 값이 다음 PC값으로 선정된다.

0이 아니면 PC +4가 target이 된다.

• Single-Cycle Datapath

| RegWrite | 목적지 레지스터에 쓸지 여부를 지정한다. |

| ALUSrc | ALU의 소스를 레지스터 데이터 또는 즉시값으로 선택한다. |

| ALUOp | ALU의 작업을 지정한다. |

| MemWrite | 메모리에 쓸지 여부를 지정한다. |

| MemRead | 메모리에서 읽을지 여부를 지정한다. |

| MemtoReg | 메모리 또는 ALU 출력 중에서 레지스터에 쓸 데이터를 선택한다. |

| PCSrc | 다음 PC값을 결정할때 PC+4 또는 분기 대상 주소를 사용한다. |

• R-Type Instruction Dataflow

| RegWrite | 1 |

| ALUSrc | 0 |

| ALUOp | OP |

| MemWrite | 0 |

| MemRead | 0 |

| MemtoReg | 0 |

| PCSrc | 0 |

• I-Type Instruction Dataflow

| RegWrite | 1 |

| ALUSrc | 1 |

| ALUOp | OP |

| MemWrite | 0 |

| MemRead | 1 |

| MemtoReg | 1 |

| PCSrc | 0 |

• S-Type Instruction Dataflow

| RegWrite | 1 |

| ALUSrc | 0 |

| ALUOp | OP |

| MemWrite | 1 |

| MemRead | 0 |

| MemtoReg | X |

| PCSrc | 0 |

• SB-Type Instruction Dataflow

| RegWrite | 0 |

| ALUSrc | 0 |

| ALUOp | OP |

| MemWrite | 0 |

| MemRead | 0 |

| MemtoReg | X |

| PCSrc | 1 |

• Single Cycle Processor의 장단점

장점

명령어 당 한 사이클로 구현하기 때문에 로직 및 구현이 단순해진다.

단점

Cycle time이 가장 느린 path(Load 명령어) 에 의해 결정되기 때문에 Clock frequency를 높이기 어렵다.

메모리 및 Functional 유닛의 활용률이 떨어진다.

다음에는 이러한 단점을 해결할 수 있는 Multicycle을 알아보도록 하자..!

'CS > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] #10 Memory(1) (0) | 2024.06.11 |

|---|---|

| [컴퓨터구조] #9 Pipeline (0) | 2024.06.09 |

| [컴퓨터구조] #7 ISA(3) (0) | 2024.04.23 |

| [컴퓨터구조] #6 ISA(2) (0) | 2024.04.23 |

| [컴퓨터구조] #5 ISA(1) (0) | 2024.04.22 |