서로 다른 종류의 저장 장치는 다른 access time을 가진다.

Random access

데이터가 어디있든지 간에 동일한 access time을 가진다.

ex) DRAM, SRAM, Flash Memory

Non-random access

데이터의 위치에 따라 access time이 달라진다.

현재는 거의 사용되지 않는다.

• Dynamic Random Access Memory (DRAM)

Data가 주기적으로 refresh 되어야 해서 Dynamic이다.

Capacitor에 전하가 충전되는 것으로 data가 저장된다.

1 트랜지스터가 전하량을 확인하는데 사용된다.

(충전되면 1, 빠지면 0)

데이터를 읽고 다시 써줘야 한다.

구멍 뚫린 양동이라고 생각하면 이해하기 쉽다.

• Static Random Access Memory (SRAM)

Refresh 없어도 전원이 공급되는 한 데이터가 유지되기 때문에 static이다.

DRAM vs SRAM

| DRAM | 높은 Density | 낮은 전력소모 | 낮은 가격 | 느림(50-70ns) |

| SRAM | 낮은 Density | 높은 전력 소모 | 비싼 가격 | 빠름(0.5-0.75ns) |

둘다 공통적으로 전원이 꺼지면 데이터가 유지된다.

• Flash Memory (SSD)

전원이 연결되어 있지 않아도 데이터가 유지된다.(비휘발성 메모리)

block 단위로 데이터가 쓰여진다.

Read-only memoty (ROM) : 공장에서 프로그래밍 되어서 나온다.

Programmmable ROM (PROM) : 한번 프로그래밍이 가능하다.

Erasable PROM (EPROM) : UV나 X-ray를 사용하여 데이터를 지우고 다시 프로그래밍 할 수 있다.

Electrically erasale PROM (EEPROM) : 전기적으로 지우고 다시 프로그래밍 할 수 있다.

Intel Optane memory : 인텔사가 만든 메모리로 DRAM 보다는 느리지만 데이터 밀도가 낮다.

• Problem

Logic가 메모리의 격차가 점점 벌어지고 있다.

따라서 현재도 DRAM을 대체할 것을 많이 찾고 있다고 한다.

결국 문제는 항상 CPU가 쉬지 않고 일하게 하는 방법을 찾는 것이다!

빠른 메모리는 비싸고 느린 메모리는 성능을 비싸기 때문에

두 종류의 메모리를 모두 활용하는 Hybrid solution을 사용한다!

따라서 자주 사용되는 데이터는 빠르고 비싼 메모리(cache)에 저장하고 나머지는 느리지만 저렴한 메모리에 저장한다.

• Locality (지역성)

90%의 Access가 전체 address 중 10%에서만 이루어진다.

(= 쓰는것만 쓴다는 소리)

실제 이 현상을 활용하는 것이 매우 유용하다.

Temporal locality (시간적 지역성)

만약 어떤 data가 최근에 사용되었다면, 곧 다시 사용될 가능성이 높다.

Spatial locality (공간적 지역성)

만약 어떤 data가 최근에 사용되었다면, 그 주변에 있는 data가 곧 사용될 가능성이 높다.

• Solution

따라서 메모리를 계층적으로 정렬하여 사용하여 빠른 메모리를 대부분의 시간동안 사용하도록 하는 것이 목표이다.

• Caches

캐시는 크지만 느린 Storge(DRAM, Flash)의 Buffer로 사용되는 중간단계 Storage component이다.

대부분의 컴퓨터 시스템은 다중 캐시를 사용한다.(L1~L3)

가능한한 저렴한 메모리를 많이 사용하면서 가장 빠른 접근 성능을 제공하는 것을 목표로 한다.

또한 Cache는 하드웨어 설계에만 국한되는 아이디어가 아닌 소프트웨어 개발자에게도 중요한 아이디어이다!

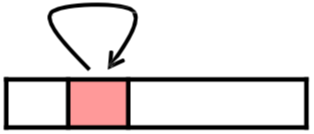

Upper level 캐시

프로세서에 가까운 메모리(= 비싸고 빠른 메모리)

Lower level 캐시

프로세서에서 멀리있는 메모리(= 느리고 싼 메모리)

Block : 서로 다른 계층 사이에서 주고받는 데이터의 단위

데이터가 해당 level 캐시에 존재한다. → Hit

데이터가 해당 level 캐시에 없다. → Miss

Hit rate가 높을수록 좋다.

공간적 지역성 : 연속적인 words로 구성된 block을 상위레벨 캐시에 저장한다.

시간적 지역성 : 최근에 접근한 데이터를 프로세서에 가까운 메모리에 저장한다.

Data를 쫓아내고 새로운 data를 저장할 공간을 마련할 때에도 최근에 접근된 data들이 캐시에 남아있을 수 있도록 한다.

• Access Times

Average access time = hit time + mis penalty * miss rate

Hit time은 낮고 Hit rate는 높아야 좋다.

(miss penalty는 hit time 보다 매우매우 높기 때문이다.)

cache hit인 경우, hit time이 1 cycle 이내라면 pipeline에 영향을 미치지 않지만, cache miss는 pipeline에 영향을 준다.

• Cache Arrangement

1. Direct Mapped : 메모리 주소가 캐시 특정 location에 directly mapping 된다.

2. Fully Associative : Data가 cache 내 어디든지 위치될 수 있다.

3. N-way Set Associative(hybrid) : Data가 cache 내 특정 set 안에서는 어떤 위치에든 저장될 수 있다.

• Direct Mapped Cache

각 Memory Block은 하나의 Single Cache Block에 Mapping 된다.

주소 비트의 LSB를 사용하여 인덱스 계산을 한다.

Index = Block_address & (#blocks in cache - 1)

ex) 8-1 = 7 (111이 하위 3bit로 인덱싱 된다.)

하위 2bit는 bit offset으로 항상 00이다.

32bit 기준으로 Index는 10bit, Tag는 20bit이다.

상위 bit인 Tag를 비교해서 데이터 접근을 한다.

캐시 메모리에 유효한 데이터인지를 확인하기 위해 Valid bit를 사용한다.

(유효한 데이터 = 1)

• Block Size Consideration

블록 사이즈가 커질수록, miss rate는 줄어든다.

그러나 캐시 크기가 동일한 상태에서 블록 사이즈가 커지면 블록 개수가 줄어들고, 결국 miss penalty가 증가한다.

따라서 오히려 miss rate가 줄어드는 이득을 상쇄시킨다.

'CS > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] #12 Memory(3) (0) | 2024.06.11 |

|---|---|

| [컴퓨터구조] #11 Memory(2) (0) | 2024.06.11 |

| [컴퓨터구조] #9 Pipeline (0) | 2024.06.09 |

| [컴퓨터구조] #8 Processor (0) | 2024.06.03 |

| [컴퓨터구조] #7 ISA(3) (0) | 2024.04.23 |